关于逻辑阵列的应用(从点赞美图到万能)

关于逻辑阵列的应用(从点赞美图到万能)随着集成电路的制造工艺与技术进一步发展,人们能够把更多的门电路,寄存器等功能模块放到同一个芯片当中,但这些模块之间又该怎样连接呢?如果按照张三(A用户)的需求连接,这个集成电路片就很难卖给李四(B用户),即使找到A与B用户都能接受的方案,又很难满足王二麻子(C用户)的需求。这个矛盾,随着集成电路的集成度逐步增高,变得越来越突出。►图1:早期用集成电路搭接的逻辑电路板●●●一位人品好到爆的朋友发了九张美食照片,自然是点赞无数,少不了还有许多朋友的赞美评论。“烙饼卷大葱配上小米粥令人馋涎欲滴”,“蘑菇炖小鸡是我的最爱”,“红油辣子好地道,除了吃螺狮面,我顿顿都得来一勺”,等等等等。小小的手机屏顿时好像香了不少。这些赞美,在厨艺渣渣如我的电子学老师看来,除了悄悄咽口水,还可以作为数字逻辑的好教材,用来说明一个逻辑学的定理:任何复杂的逻辑关系式,都可以分解成为一个多项式。怎么分解,我们后面会谈到(

►图源:Pixabay.com

撰文 | 吴进远(美国费米国家加速器实验室)

责编 | 陈晓雪

知识分子为更好的智趣生活 ID:The-Intellectual

●●●

一位人品好到爆的朋友发了九张美食照片,自然是点赞无数,少不了还有许多朋友的赞美评论。“烙饼卷大葱配上小米粥令人馋涎欲滴”,“蘑菇炖小鸡是我的最爱”,“红油辣子好地道,除了吃螺狮面,我顿顿都得来一勺”,等等等等。小小的手机屏顿时好像香了不少。

这些赞美,在厨艺渣渣如我的电子学老师看来,除了悄悄咽口水,还可以作为数字逻辑的好教材,用来说明一个逻辑学的定理:任何复杂的逻辑关系式,都可以分解成为一个多项式。怎么分解,我们后面会谈到(见下文第二部分)。逻辑关系式的这种性质,是人们设计“万能”数字逻辑器件的基础。对于《知识分子》广大读者,在科研工作中设计制作实验装备,这是一种非常实用的基础技能。

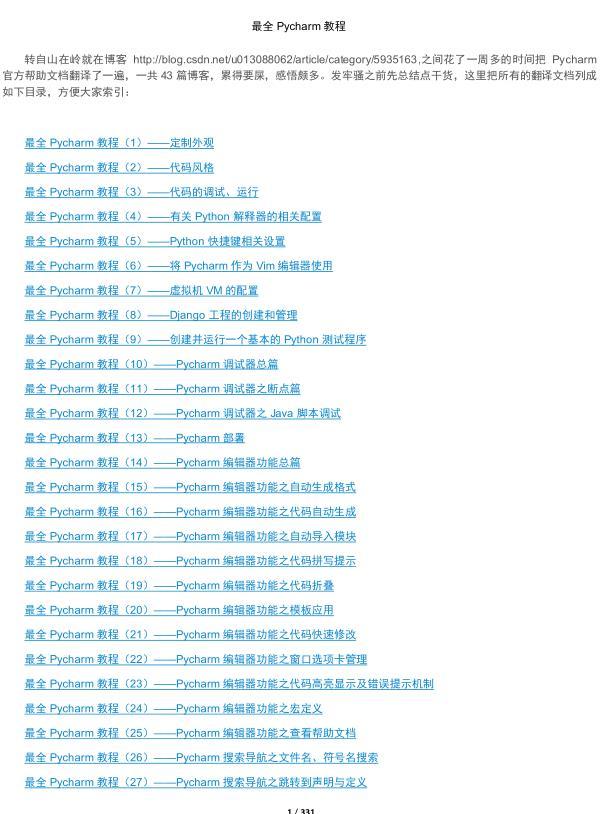

►图1:早期用集成电路搭接的逻辑电路板

随着集成电路的制造工艺与技术进一步发展,人们能够把更多的门电路,寄存器等功能模块放到同一个芯片当中,但这些模块之间又该怎样连接呢?如果按照张三(A用户)的需求连接,这个集成电路片就很难卖给李四(B用户),即使找到A与B用户都能接受的方案,又很难满足王二麻子(C用户)的需求。这个矛盾,随着集成电路的集成度逐步增高,变得越来越突出。

大家可能会说,这还不简单,每个用户按照自己的需求设计自己的集成电路就可以了嘛。这的确是一个解决方案,这种用户根据自己需求设计的集成电路叫做ASIC(Application Specific Integrated Circuit,专用集成电路)。在工业界,我们看到很多厂商都为自己的产品设计专用的集成电路,用来实现各种智能控制,通讯,计算等功能,甚至用在儿童玩具当中。

集成电路这种东西,批量生产时每一个集成电路片的成本并不太高。但是制作光刻掩模,调整设备,设定工艺参数等一次性成本非常高。因此,只有在大批量生产的情况下,才能将一次性成本分摊开,实现经济上的可行性。

在科学研究领域,各种实验装置大多数情况下都不会复制成千上万套,因而往往用不起专用集成电路。仅仅在核物理,高能物理当中,由于探测器需要很多通道,因此探测单元信号的放大,处理以及数字化的功能有一定的可能用专用集成电路来实现。

除了在科研领域,即使是在工业界,对于逻辑电路也存在很多小批量的需求。这种需求,促成了“万能”或者通用的可编程逻辑器件的出现。

怎样达到万能?回到朋友圈里的九张美图,我们可以详细地分析一下这些赞美的评论。“烙饼卷大葱配上小米粥令人馋涎欲滴”,“蘑菇炖小鸡是我的最爱”,“红油辣子好地道,除了吃螺狮面,我顿顿都得来一勺”,等等等等。

这些赞美,每一条都可以看成一个复杂的逻辑关系多项式中的一项。这个多项式中的每一项,是用“与”(and)运算连接起来的输入变量。而所有这些项又由“或”(or)运算连接成为多项式。此外,多项式中某些输入变量可能会先经过一个“非”(not)运算然后再参与其它运算。“与”运算相当于代数多项式中的乘法,“或”运算相当于加法,而“非”运算相当于负号。

比如前面朋友圈的评论就可以写成如下逻辑多项式:

好吃 = (烙饼 and 大葱 and 小米粥)

or (蘑菇 and 小鸡)

or (红油辣子 and (not(螺狮 and 面条)))

上面这个关系式中的第三项,实际上还可以做进一步的分解。为了简化问题,我们忽略烹调方法,把含有螺狮与面条这两种食材的食物叫做螺狮面,也就是说,螺狮面是含螺狮的食物与含面条的食物这两个集合的交集。那么什么食物不是螺狮面呢?不是螺狮面的食物属于不含螺狮食物这个集合或者不含面条食物这个集合。因此:

(not(螺狮 and 面条))=(not(螺狮))or (not(面条))

大家可能听说过德·摩根定理吧,德·摩根定理是一对关系式,上面这个关系式是其中的一个。除了这个“非与变或”关系式之外,还有一个“非或变与”关系式。有兴趣的读者可以上网搜索“De Morgan's laws”,以获得更多信息。

利用德·摩根定理,前面朋友圈的评论就可以最终展开成为:

好吃 = (烙饼 and 大葱 and 小米粥)

or (蘑菇 and 小鸡)

or (红油辣子 and (not(螺狮)))

or (红油辣子 and (not(面条)))

复杂逻辑关系式能够分解为多项式,这个数学结论为我们设计通用逻辑电路器件指出了方向。

FPGA的前身:PAL与GAL人们最早开发的通用逻辑器件:可编程阵列逻辑(PAL)就是基于前面谈到的逻辑多项式性质设计的。图2是PAL的原理图。

►图2:可编程阵列逻辑(PAL)的原理图

一个PAL器件可以接收多个逻辑电平输入,每个输入信号驱动两路纵向信号线。一路保持原有逻辑电平,输入为高电平时,输出也是高电平,而当输入为低电平时,输出也是低电平。第二路信号通过一个反相器,将逻辑电平翻转,输入为高电平时,输出变成低电平,输入为低电平时,输出为高电平,也就是说,对输入信号作了“非”运算。

这样,N个输入信号一共驱动2N根纵向的信号线,根据用户需要它们选择性地与横向的逻辑线连接。(这里谈到的连接实际上是通过一个二极管或者三极管连接的,为了简洁,我们没有把相应电路的细节画出来。)

每一根横向的逻辑线实现一个“与”门功能,也就是说,所有与之连接的信号都必须同时为逻辑“1”,其输出才是“1”。这样,每一根横向的逻辑线就成为逻辑关系式中的一项。若干根(通常是8根)横向逻辑线的输出送入一个“或”门,这样,这个“或”门的输出,就成为一个逻辑多项式的结果。

PAL器件出厂的时候,所有纵向线与横向线的交点都是连接在一起的。用户根据自己的需要,将不需要的连接点切断,仅保留需要的连接点,这个过程就是编程。这样,PAL就成为一个“万能”的逻辑器件,可以满足不同用户的需求。

最早的PAL器件,有些产品曾经使用低熔点的金属做连接点,用户编程的时候,把不需要的连接点熔断。人们把这样一个编程的过程叫做把程序“烧”入器件,这种说法一直沿用到现在。这样的器件显然无法多次编程,只能搞一锤子买卖。这与早期的可编程只读存储器(PROM)的情况类似。

很快,可擦除只读存储器(EPROM)和电子可擦除只读存储器(EEPROM)的技术被推广到PAL的领域,从而出现了可以多次重复编程的逻辑阵列器件。对这样的器件,人们使用了另一个名字:通用阵列逻辑GAL。

用户使用PAL或GAL时,先用专门的语言将需要的逻辑关系式写成一个文本文件,然后用专门的计算机软件将逻辑关系式简化展开成为多项式,并根据器件的构造,确定在器件内要保留的连接点。随后,我们把编译出来的结果“烧”入器件,器件就具备了我们需要的功能,可以焊到电路板上了。

这类可编程阵列逻辑器件已经有30多年的历史了,一般来说,历史这样悠久的电子技术很早之前就应该过时淘汰了。不过,我最近在一些电子产品供应商的网站上搜索,发现尽管由于注册商标的限制,人们已经不再使用PAL与GAL这两个名字,但仍然有厂家在生产销售类似的可编程器件。在实际工作中,使用这类可编程逻辑器件在电路板上来实现一些简单的逻辑电路还是十分方便的。

FPGA的构造前面谈到的可编程阵列逻辑器件仅仅能在一定的限度内实现万能的逻辑应用,有时候,比如当逻辑关系多项式的项数超过8个,现有的器件就不能适应了。这就需要我们寻找更加万能的逻辑实现方法。

此外,现代的PAL或GAL器件虽然理论上可以擦除原有的内容重新编程,可是实际上一旦焊到电路板上,要想修改,就得把它们烫下来,重新编程,再重新焊回到电路板上,非常麻烦。(不过,作者确实见过别的同事不幸地做过这样的事情。)因此使用PAL或GAL这类器件基本没有后悔药可以吃。而当一个器件中晶体管数量进一步增加后,没有人能一次就把复杂的逻辑功能设计对,这就需要为用户提供后悔药,让器件可以在焊到电路板上之后仍然可以随时重新编程与设置,也就是说,要做到现场可编程。于是人们就设计出了现场可编程门阵列(field-programmable gate array FPGA)器件。

这种更加万能的逻辑实现方法是基于查询表(LUT)的,几乎所有主流FPGA产品都是用查询表来实现逻辑功能的。大多数FPGA产品里用到的查询表包括四根或六根输入线,一根输出线。

在实际器件中,每一个查询表的后面都有一个寄存器(DFF),组成一个逻辑单元,如图3所示。

►图3:FPGA的逻辑单元

这个寄存器的作用,是将查询表输出的逻辑电平暂存,然后送到下一级的逻辑单元。这样,我们在FPGA中就可以组成多个层级的逻辑处理流水线,通过一定的时序,实现更加复杂的逻辑或计算功能。

所谓查询表实质上是一个小小的存储器,对于一个4输入(或6输入)的查询表,里面有16个(或64个)存储单元,每个存储单元包含一个比特。查询表的输入线是存储器的地址线,根据这几根输入线的不同逻辑组合,存储器指向相应的存储单元,将预先存在那里的比特信息读出,驱动输出端,从而生成需要的逻辑功能。

查询表真的是万能的吗?真的能生成任何逻辑功能吗?对于查询表的每一个输入端,它只可能有两个逻辑电平,低(0)或高(1)。因此,对于4个输入的查询表,最多只可能存在16个输入逻辑组合。而对于每一个逻辑组合,逻辑单元的输出值,不外乎只有0或1两个可能。因此,不管我们需要生成多么复杂的逻辑关系式,只要在16个存储单元当中预先存入相应的0或1数据就可以了。

我们通过下表列出的几个例子,来说明这个方法。顺便介绍一下,这种形式的表叫逻辑真值表(Logic Truth Table)。

表中,ABCD是4根输入线对应的逻辑组合,一共有16个。AND4是4输入的“与”门逻辑,4根输入线必须全部是1时,输出才是1,否则是0。而OR4是4输入的“或”门逻辑,4根输入线任意一个是1时,输出就是1,只有4根输入线全部是0时,输出才是0。

第三列的M3V1是一个比较复杂的逻辑关系式,可以称为多数及否决逻辑。在BCD这3根输入线中,必须有2根以上输入为1,同时输入线A也必须不是0,或者BCD全是1,整个逻辑关系式的输出才是1。这很像一个公司里董事会表决一个议案,要想通过议案,普通董事会成员(BCD)必须表决达到简单多数赞成,但董事长(A)却有一票否决权。不过,如果普通董事会成员一致通过,则董事长否决也没有用。大家仔细分析前面这个真值表,就可以看清楚这个逻辑。

读者可能会好奇,像这样一个查询表能够生成多少种不同的逻辑关系式呢?我们看到,这个查询表当中有16个存储单元,每个单元存储一个比特的数据,可以取0或1两个数值。因此,16个存储单元中存储的数据可以有2^16 = 65536种不同的组合,每一种组合实质上是一种逻辑关系式的表述。当然,我们这里假定4根输入线不可以互相交换,如果考虑逻辑关系当中的交换律,不同逻辑关系的总数就没有那么多了。这个总数的计算有点复杂,但我们至少知道,这样一个查询表足以表述任何一个四输入端(或三、二输入端)的逻辑关系式。

FPGA器件中有很多是基于RAM(随机存储器)的,一旦关掉电源,里面的内容就全部丢失了。因此,每次接通电源后,必须把存在计算机或者电路板上其它器件里的数据重新加载到FPGA中,把用户需要的逻辑写入查询表里,FPGA才能按照用户的要求工作。从这点看,FPGA不仅是可以实现现场可编程,而且是必须能够现场可编程才能正常使用。FPGA里需要的这些设置信息,通常是通过器件上的几个专用引脚,用串行数据的编码方式送进去的。

FPGA与微处理器的异同有的读者可能会质疑,投票表决这样一个事为什么要这样复杂呢?一张票一张票地数一下不就行了吗?

这是一个很好的问题,它揭示了微处理器技术与可编程逻辑器件技术这两大领域中思维方式的不同。

一张张地数,是微处理器的做法,其特点是,将一个复杂的功能拆解成许多步骤,每个步骤的处理却非常简单。这样,我们可以利用微处理器中相对简单,可塑性很差的处理单元,通过复杂而多步骤的程序,来实现复杂的功能。我们用到的计算机,智能电子产品等,都是按照这样一个技术路线设计的。

而对于可编程逻辑器件,我们尽量将复杂的功能扁平地展开。对于复杂度比较高的功能,我们通常会把它们安排到若干级流水线当中。

这样做虽然比较麻烦,但可以很方便地将多个数据计算或逻辑处理功能并行实现,因而处理速度可以比同等的微处理器快。比如前面讨论的表决问题,用微处理器至少要4个时钟周期,而用FPGA则只需要一个时钟周期就能得到结果。固然,微处理器的时钟周期很短,一般仅有几个纳秒。但在有些应用中,我们真的是等不起这几个时钟周期,比如对于一个像加速器这样的大型科研设备,一旦某些子系统出现故障就要立即进入停机保护状态,这就要求相应的保护系统判断速度越快越好。

实际上,我们这里谈到对PAL或FPGA的“编程”,只是一个历史上形成的,不很确切的术语。我们加载到FPGA中的固件并不是“程序”,而是对FPGA中各个逻辑单元功能,以及它们之间连接的电路描述。这种描述通常可以用专门的语言写成,其中每一部分的次序往往可以任意安排,毕竟对于一个电路,先描述哪一块后描述哪一块并没有实质的区别。相反。我们为微处理器所编写的是真正的程序,程序中的每一行对应于微处理器所执行的每一个处理步骤,通常这些步骤的先后顺序是不可以随便颠倒的。

FPGA的实际应用在科学实验当中,FPGA可以适应很多不同的应用需求。当然,它的应用也多少有点儿门槛,不过这个门槛相当低。一个用户在电脑上下载安装一个编译软件,再花200美元左右买个验证板,如图4所示,就能做很多事情。

►图4:一种入门级的FPGA器件验证板

作者带过不少高中生,他们往往花几天到一周时间,就能学会初步的编程技能,让FPGA控制发光二极管发出各种花样的闪光,控制扬声器唱歌。下面的视频显示在验证板上加载了这种固件后的运行情况。

点击链接观看视频:

https://v.qq.com/iframe/player.html?vid=q1337ongc1d&width=670&height=376.875&auto=0

期待这篇文章,能帮助需要的读者跨过应用的门槛。

制版编辑:黄玉莹 |

本页刊发内容未经书面许可禁止转载及使用

公众号、报刊等转载请联系授权

zizaifenxiang@163.com

知识分子为更好的智趣生活 ID:The-Intellectual